Студентам > Курсовые > Разработка цифрового таймера

Разработка цифрового таймераСтраница: 4/5

Если на вход "–1" подается импульсный перепад от низкого

уровня к высокому, от

содержимого счетчика вычитается 1.

Аналогичный перепад, поданный на вход +1, увеличивает счет на 1. Если для счета используется один из этих входов, на

другом тактовом входе следует

зафиксировать напряжение высокого логического

уровня. Первый триггер счетчика не может переключиться, если на его тактовом

входе зафиксировано напряжение низкого уровня. Во избежание ошибок менять

направление счета следует в моменты, когда запускающий тактовый импульс перешел на высокий уровень,

т. е. во время плоской вершины импульса.

На выходах ">9" и

"<0" нормальный уровень—высокий. Если счет

достиг максимума (цифра 9), с приходом

следующего тактового перепада от высокого уровня к низкому на вход +1 (более 9)

на выходе ">9" появится напряжение низкого уровня. После возврата напряжения на тактовом входе

"+1" к высокому уровню, напряжение на выходе ">9"

останется низким еще на время, соответствующее двойной задержке переключения логического

элемента ТТЛ.

Аналогично на

выходе "<0" появляется напряжение низкого уровня, если на вход "-1" пришел счетный перепад низкого уровня.

Импульсные перепады от выходов

">9" и "<0" служат, таким образом, как тактовые для

последующих входов "+1" и "-1" при конструировании счетчиков более высокого порядка. Такие многокаскадные соединения

счетчиков ИЕ6 не полностью

синхронные, поскольку на последующую микросхему тактовый импульс передается с двойной задержкой

переключения.

Если на вход разрешения параллельной

загрузки Е (вывод 11) подать

напряжение низкого уровня, то код, зафиксированный ранее на параллельных входах

DO—D3 (выводы 15, 1, 10 и 9), загружается в счетчик и появляется на его выходах

QO—Q3 (выводы 3, 2, 6 и 7) независимо от сигналов на тактовых входах. Следовательно, операция параллельной загрузки — асинхронная.

Параллельный запуск триггеров запрещается, если на вход сброса

R (вывод 14) подано напряжение высокого уровня. На всех выходах

Q установится

низкий уровень. Если во время (и после) операций сброса и загрузки придет тактовый перепад (от Н к В), микросхема

примет его как счетный.

Счетчики К555ИЕ6 потребляют ток

34 мА. Максимальная тактовая частота 25 МГц. Время задержки распространения

сигнала от входа "+1" до выхода ">9" 26 ns, аналогичные задержки от входа Е до выхода

Q3 составляют 40 ns. Время действия сигнала сброса (от входа R до выходов Q) 35 ns.

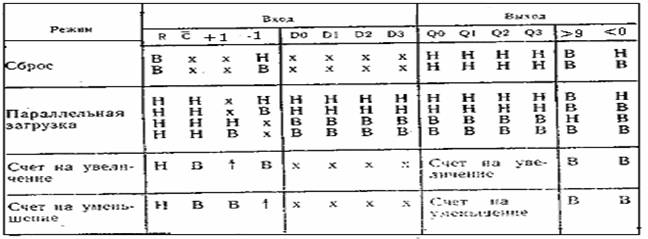

На рис. , показана

диаграмма работы десятичного счетчика ИЕ6, где обозначены

логические переходы сигналов при счете на увеличение и уменьшение. Кольцевой счет возможен в пределах 0...9, остальные шесть состояний триггерам запрещены. Составив определенную комбинацию входных сигналов, по табл. можно выбрать один из четырех режимов работы счетчика ИЕ6. Счет

на увеличение здесь закончится при

выходном коде ВННВ (9), на уменьшение — при НННН (0).

Рис.

Табл.

3) Блок

индикации.

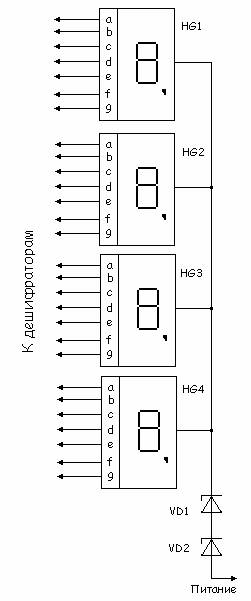

Для индикации состояния СВВ были

использованы семисегментные индикаторы типа АЛС324Б. Схема соединения

индикаторов показана на рис.

Рис.

При конструировании устройства индикаторы

устанавливаются на передней панели, слева направо, начиная с HL1. Стабисторы D1 и D2 служат для предотвращения

перегрузки преобразователя кода. Принцип их действия заключается в том что

напряжение источника питания +5V распределяется между тремя сопротивлениями

нагрузки и сопротивлениями D1 и D2,

сопротивлением сегмента индикатора и сопротивлением транзисторного ключа

микросхемы. Поскольку суммарное падение напряжения на сегменте индикатора и

ключа микросхемы не должно превышать 2 – 2,5 V

(при этом ток через эти элементы будет в пределах допустимого), в большинстве

подобных схем раньше использовался ограничительный резистор, который

устанавливался в разрыв провода между микросхемой и индикатором. При этом на

каждый индикатор требовалось 7 таких резисторов.

Установить один общий резистор мешала его

линейность, из–за которой, например, цифра 1 светилась очень ярко, а цифра 8

была практически не видна. Использование нелинейных элементов (стабисторов)

позволило решить эту проблему. Благодаря нелинейной ВАХ падение напряжения на

них остается практически постоянным, независимо от количества горящих сегментов,

и поэтому яркость всех цифр одинакова. Применение такой схемы питания

индикаторов позволило отказаться от использования 28 резисторов.

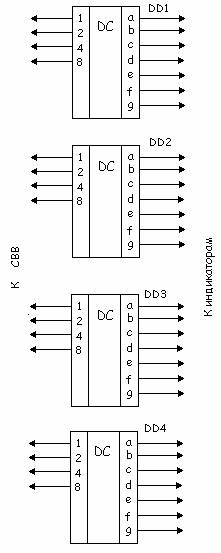

2) Преобразователь кода.

Преобразователь кода предназначен для

перевода двоично – десятичного кода с выходов разрядов СВВ в код семисегментных

индикаторов. Принципиальная схема этого блока показана на рис.

Рис.

Он состоит

из четырех специализированных микросхем этого КР514ИД1. На входы этих микросхем

подается четырех разрядный двоично – десятичный код а выходы подключаются к

соответствующим разрядам индикатора. Как видно из схемы для управления

индикатором применяется статический метод. Это позволило значительно упростить

устройство индикации, хотя и потребовало использование большого количества

соединительных линий. (28 штук).

Состояние выходов микросхемы

КР514ИД1, сведены в таблицу.

Блоки управления

________________________________________________________________

1 ) Схема

обнуления.

Принципиальная схема блока обнуления

приведена на рис. Она состоит из 2 логических элементов DD1 и DD2 микросхемы К555ЛАЗ, причем элемент

DD2 используется в качестве инвертора. Рассмотрим работу схемы.

Рис.

При первоначальном включении устройства

конденсатор С1 заряжается через резистор R1. При этом в течении некоторого времени

(порядка 0,1 секунды), на входе 2 DD1 присутствует

логический ноль. В результате на выходе этого элемента устанавливается

(независимо от состояния входа 1) логическая единица. Она подается на входы

R микросхем СВВ, в результате чего последний обнуляется. Элемент

DD2 необходим, поскольку входы сброса СН, РЗ и БУПУ в отличие от

аналогичных входов СВВ, инверсные. Клавиша «Сброс» клавиатуры подключается

параллельно конденсатору С1, а импульс сброса от СВВ подается вход

1. Это необходимо для того, чтобы время срабатывания схемы обнуления, которое

складывается с временем выдержки, было минимальным и не оказывало на него

существенного влияния .

После обнуления на выходе “окончание счета”

СВВ и следовательно, на входе 1 DD1

устанавливается логическая единица, если конденсатор С1 заряжен а

клавиша «Сброс» не нажата то схема перейдет в режим ожидания. На выходе “сброс

СВВ” установится логический ноль разрешающий его работу. Конденсаторы С2

и С3 предназначены для предотвращения ложного срабатывания схемы из

– за помех. Их емкость должны относиться между собой как (50 – 100) * С3 =

С2, а максимальная емкость С2 выбирается так, чтобы время

ее зарядки не оказывало заметного влияния на точность интервала выдержки.

2) Схема управления

Принципиальная схема этого блока приведена на рис.

Он

построен на одном из триггеров микросхемы К555ТМ2 и трех логических элементах

микросхемы К555ЛА3. Характеристики этих микросхем были даны выше.

Блок предназначен для синхронного управления РЗ и ДПЗ. На вход “Тактовые

импульсы” подаются импульсы с ТГ. Благодаря инвертору на элементе

DD1 триггер переключается по спаду импульса.

Рис.

Для

блокировки работы блока и следовательно окончания загрузки чисел с клавиатуры

используется вход S триггера.

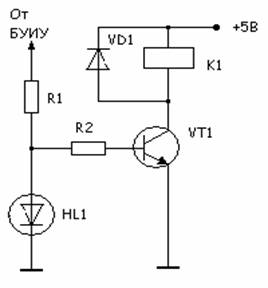

3) Исполнительное устройство.

Исполнительное устройство должно

обеспечивать включение нагрузки на время выдержки или по прошествии этого

времени. Принципиальная схема этого блока представлена на рис.

Рис.

Светодиод HL1

служит для индикации включения нагрузки. Помимо этого он, совместно с

R1 выполняет роль делителя напряжения. С выхода этого делителя

через резистор R2 напряжение подается на базу транзистора

VT1 и открывает его. Резистор R2

ограничивает ток базы транзистора и, тем самым, предотвращает его влияние на

БУИУ. Его сопротивление необходимо выбирать по возможности больше. В нашем

случае оно было подобрано экспериментально и равно 10 кОм. В коллекторную цепь

транзистора включается реле К1, которое своими контактами управляет нагрузкой.

Диод VD1 необходим для замыкания токов самоиндукции,

возникающих в обмотке реле при запирании транзистора. Тем самым он

предотвращает пробой транзистора, а также возникновение помех по цепи питания

микросхем. Сопротивление резистора R1 выбрано

экспериментально, по приемлемой яркости свечения светодиода.

4) Блок

управления исполнительным устройством.

Блок управления исполнительным устройством

выполняет следующие функции:

-

включает исполнительное устройство в

начале интервала выдержки

-

выключает исполнительное устройство

после окончания выдержки

-

отключает исполнительное устройство при

нажатии на клавишу «Сброс»

-

воспринимает нажатие на клавишу «Пуск» и

подает сигнал управления на устройство блокировки.

Принципиальная схема этого блока

приведена на рис.

Рис.

На триггере DD1 построено устройство управления схемой

блокировки. Вход D триггера подключается к третьему разряду

CH. После четырех нажатий клавиш сюда подается логический ноль,

разрешающий запуск отсчета времени. К входу С подключается клавиша «Пуск»

клавиатуры. Когда эта клавиша не нажата, на С установлен логический ноль благодаря

резистору R1. При нажатии на клавишу «Пуск» перепад 0–1

на входе С разрешает запись информации (нуля) на выход триггера и,

следовательно разрешает прохождение импульсов делителя частоты к СВВ.

Вход S подключается схеме обнуления параллельно входу

обнуления СН. На элементах DD1 – DD5 собрано

устройство контроля, управляющее нагрузкой. После включения устройства в сеть

или нажатия на клавишу «Сброс» триггер DD5

устанавливается в нулевое состояние. На вход D

при этом подается логическая единица. Эта единица также устанавливается и на

одном из входов элемента DD2, выполняющего в данном случае электронного

ключа. После разблокирования схемы блокировки первый перепад 0–1 появившийся на

ее выходе, пройдет через элементы DD2, DD3 и диод VD2 на вход с триггера. Триггер переключится в

единичное состояние и подаст логическую единицу на исполнительное устройство.

Логический ноль с его инверсного выхода поступит на DD2

и запретит прохождение через него следующих импульсов. В этом состоянии

устройство будет находится до окончания счета, либо до нажатия на клавишу

“Сброс”. По окончании счета логический ноль с соответствующего выхода СВВ

поступит на входы элемента DD4, играющего роль инвертора, и далее через

VD1, на вход С триггера. Логический ноль со входа

D перепишется на выход триггера и отключит исполнительное

устройство. Элементы VD1, VD2 и

R2 представляют собой простейший логический элемент ИЛИ. Их

применение позволило отказаться от микросхемы с элементами ИЛИ и обойтись

имеющимися лишними элементами микросхемы К555ЛАЗ. Сопротивление резистора

R2 подобрано экспериментально и равняется 2,7 кОм.

Характеристики использованных микросхем К555ТМ2 и К555ЛА3 приведены выше.

Генераторное оборудование

________________________________________________________________

1) Тактовый

генератор

Тактовый

генератор является одним из основных элементов цифрового таймера. От точности

установки частоты этого генератора зависит точность интервала выдержки.

В

цифровых таймерах применяют, как правило, высокостабильные кварцевые

генераторы, которые устанавливают в специальные термостатирующие устройства,

поддерживающие постоянную температуру окружающей среды.

Точность

воспроизведения заданного временного интервала зависит также от частоты

генератора. Чем она больше, тем больше коэффициент деления делителя частоты, и

следовательно, тем больше делится значение погрешности установки частоты.

Кварцевые

генераторы можно классифицировать по различным признакам.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50